# Designing Switched-Mode Power Supplies in the High di/dt Era

Application Engineer / Keysight Technologies

Jason CHEN

## Trends in Switched-mode Power Supplies (SMPSs)

#### **Customer Demands:**

- Smaller size

- Lighter weight

- Higher switching speed (high di/ft)

- New technologies (accurate modeling)

A magical shrinking machine doesn't exist!

#### Impact:

- Performance

- Reliability

- Development/time to market costs

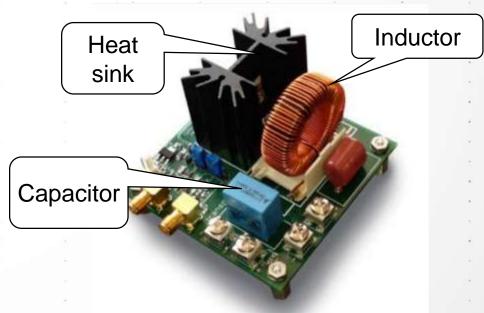

## Challenges in power circuit design

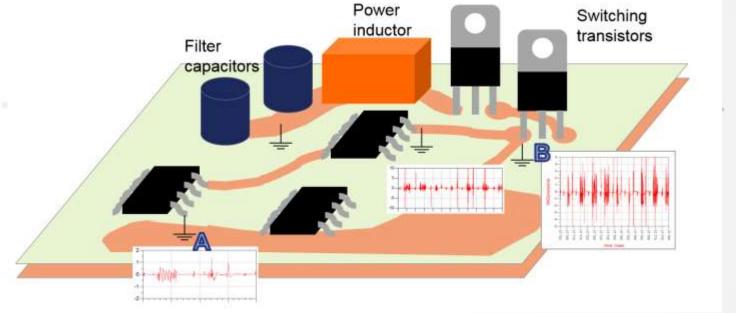

High switching frequency along with high frequency components in waveform causes unexpected EMI

Prototype circuit explosion due to unexpected surge

High switching frequency and associated surge/ringing causes malfunction

Lack of power circuit simulation tool.

Conventional tool may work for low frequency circuit but not for WBG device circuit

## **High Speed Power Converter Challenge**

#### THINKING IN THE FREQUENCY DOMAIN

## High speed power converters have relevant energy in the multi-GHz range!

KEYSIGHT TECHNOLOGIES

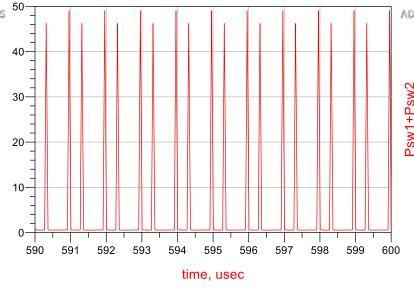

## **Higher Frequency Can Lead to Higher Switching Loss**

#### UNLESS THE EDGE SPEED IS INCREASED AS WELL

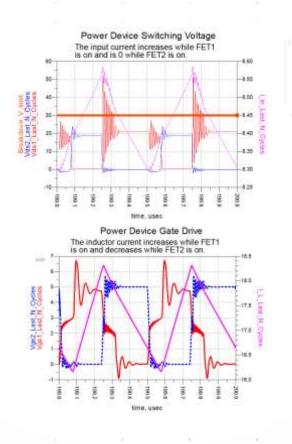

Low frequency Slow edges Switching loss 3.5% Higher frequency Same slow edges Switching loss 15.3% Higher frequency Faster edges Switching loss 3.3%

If you want to *reduce* switching loss, you have to improve the edge speed *even more dramatically* than improving the switching frequency

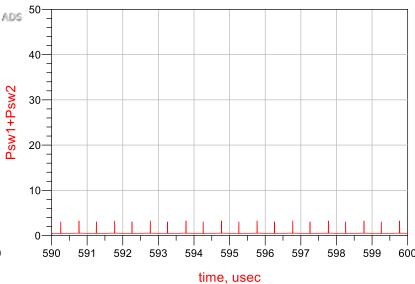

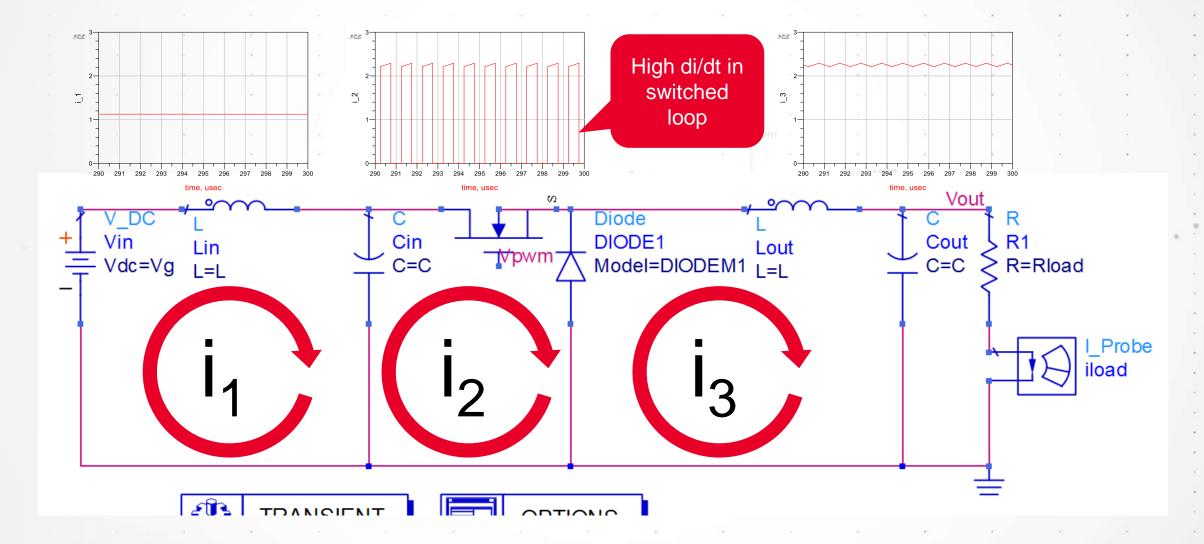

## **Current Loops: Schematic View**

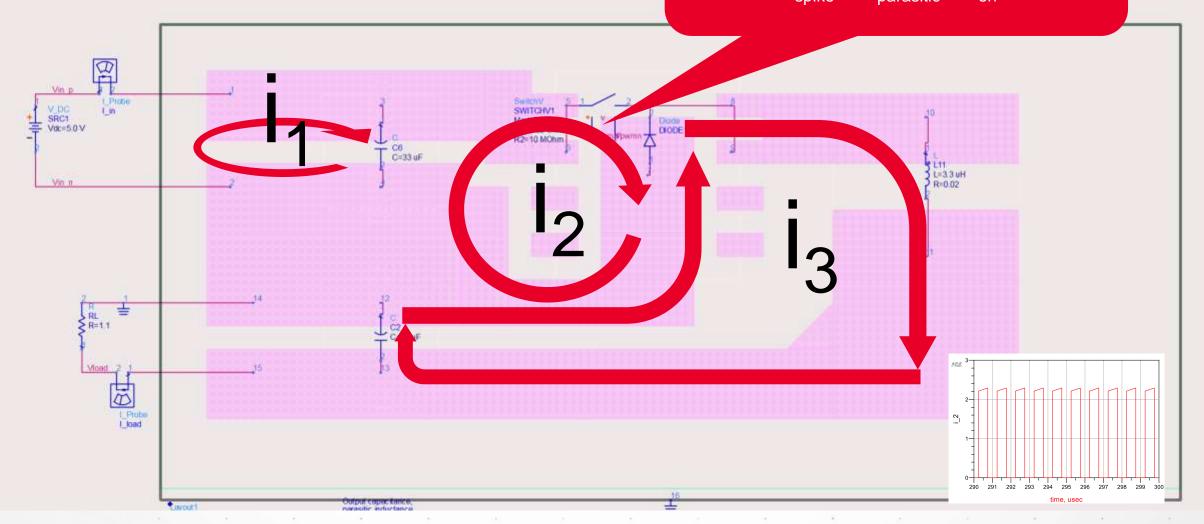

## **Current Loops: Layout View**

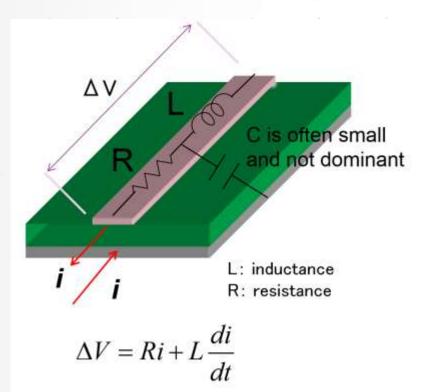

When does the layout of the switched loop become important?

$$V_{\text{spike}} = L_{\text{parasitic}} * \text{di/dt}$$

$V_{\text{spike}} = L_{\text{parasitic}} * I_{\text{on}}/\tau$

$$V_{spike} = L_{parasitic} \frac{I_{on}}{\tau}$$

$$\frac{V_{spike}}{V_{off}} = L_{parasitic} \frac{I_{on}}{\tau V_{off}}$$

$$10\% = L_{10\%} \frac{I_{on}}{\tau V_{off}}$$

$$L_{10\%} = \frac{0.1\tau V_{off}}{I_{on}}$$

Definition of inductance Linear ramp di/dt

Divide both sides by Voff

What inductance will give us a overstress spike that is, say, 10% of Voff?

Rearrange, plug in some numbers 10 ns, 20V, 4A answer is 5 nH Few mm of wire is 5 nH!

## **Traditional Low Speed Design Approach**

### PRE-LAYOUT SPICE, THEN "CUT AND TRY"

Pre-layout schematic SPICE simulation:

"Best Case" performance

First prototype has some excess ringing. Cut-and-try until "best case" approached

2-6 spins \$6k-\$60k/spin 3-8 weeks slip/spin

Image courtesy of ST Microelectronics

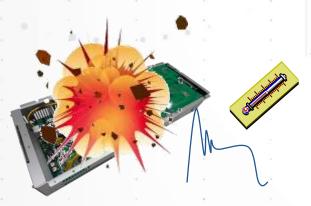

## Traditional Design Approach Applied to High Speed

### PRE-LAYOUT SPICE, THEN "CUT AND TRY"

Pre-layout schematic SPICE simulation:

"Best Case" performance

First prototype has destructive failure.

# What next?

Kevsiaht World

## A suggested Design Approach

#### **IDENTIFY AND FIX PROBLEMS BEFORE FABRICATION**

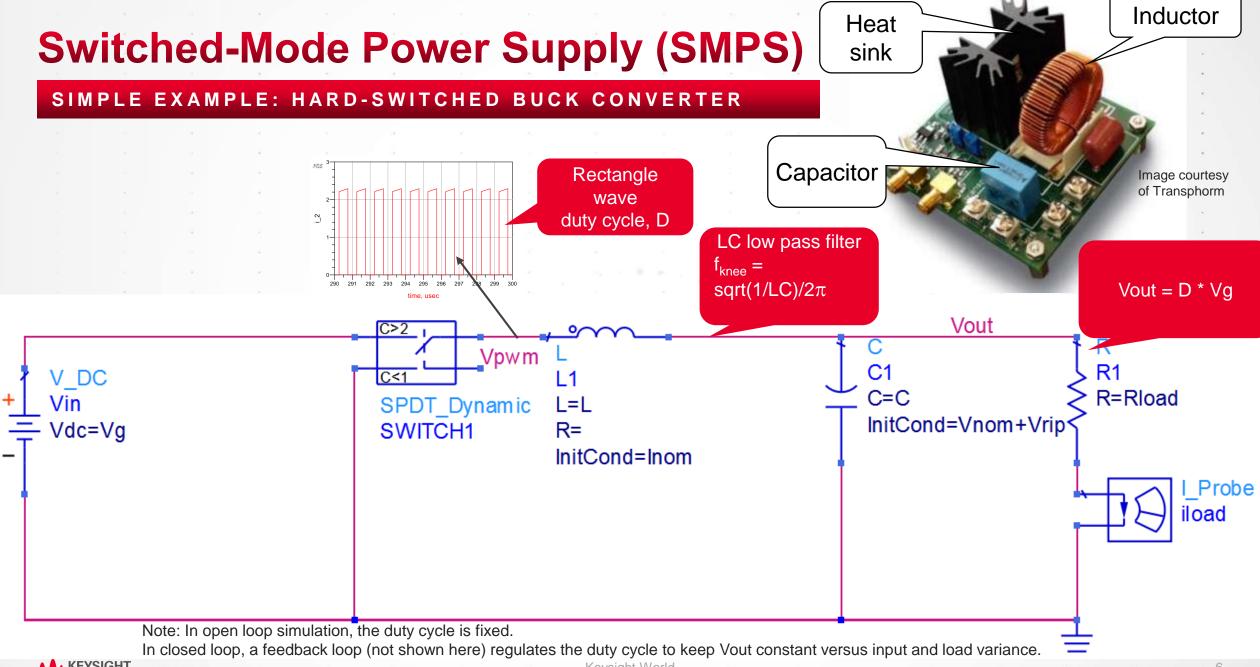

## Schematic Only Simulation (Best Case)

KEYSIGHT

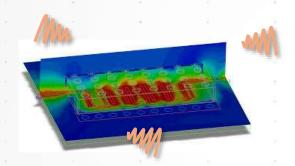

## Identify & Fix Physical Design Issues with EM

#### Final EM Verification

13

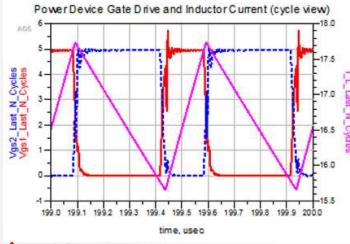

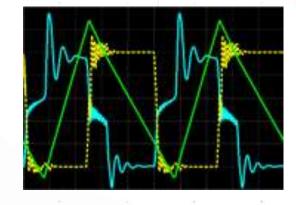

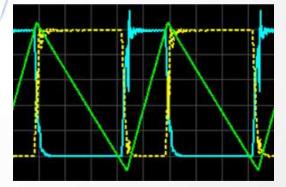

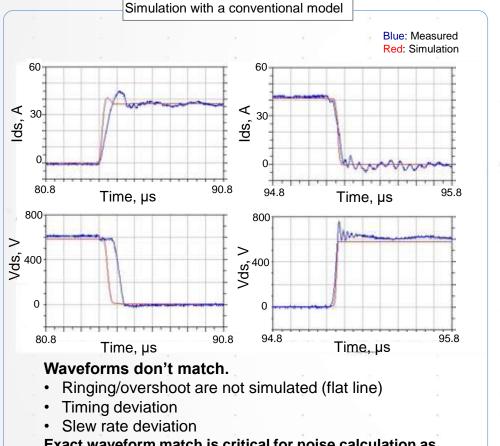

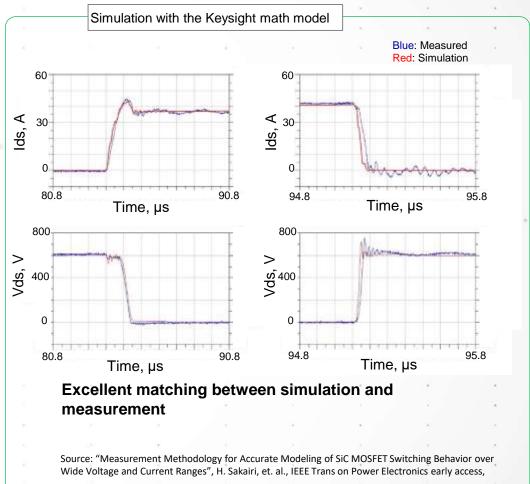

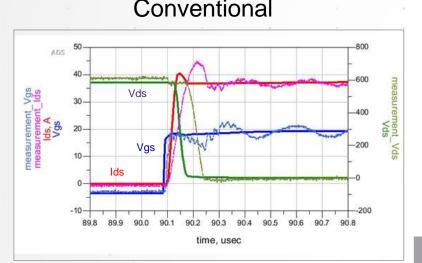

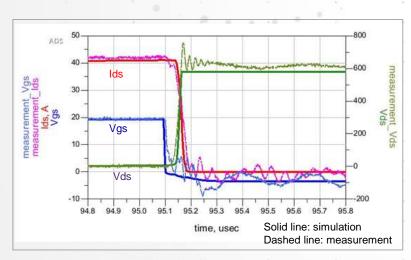

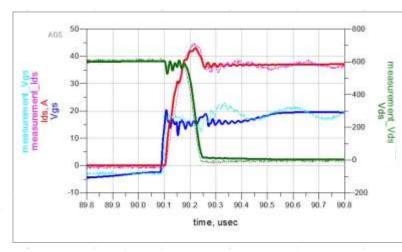

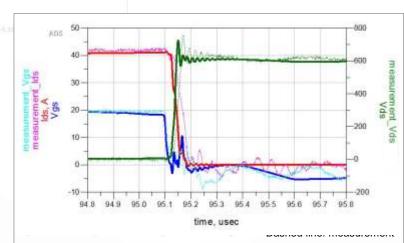

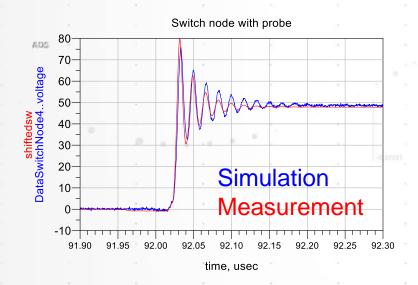

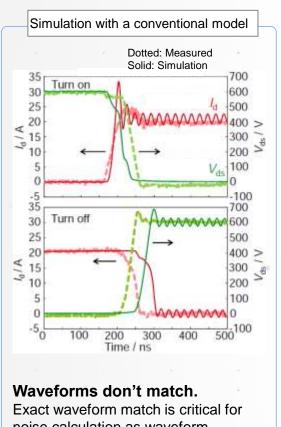

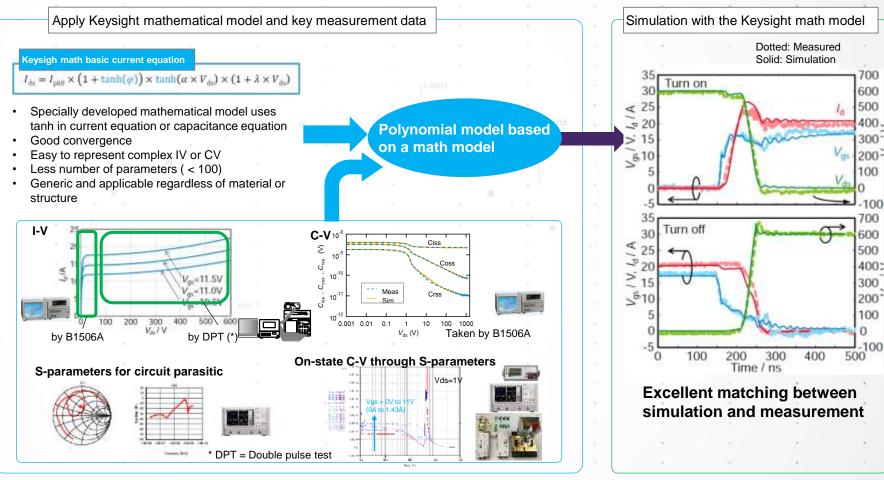

## Conventional simulation vs. New Keysight simulation method

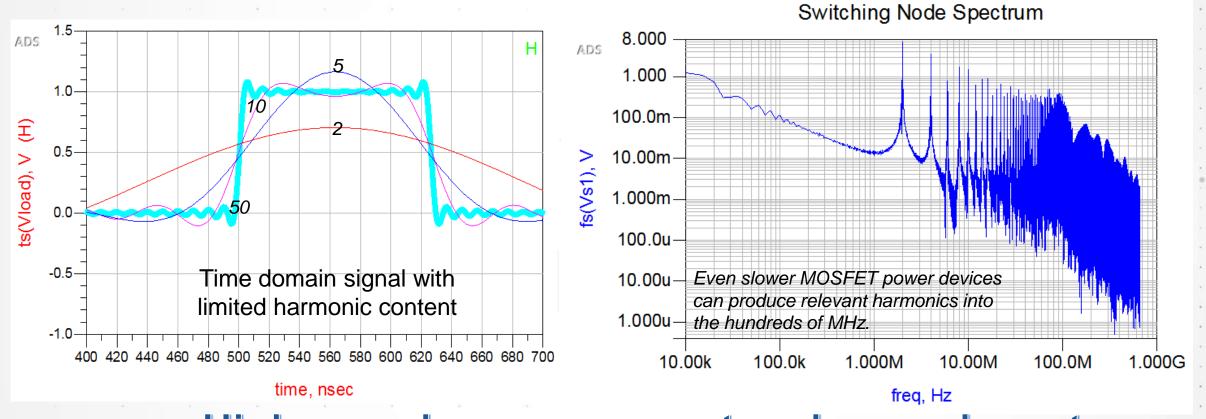

Exact waveform match is critical for noise calculation as waveform contains high frequency components

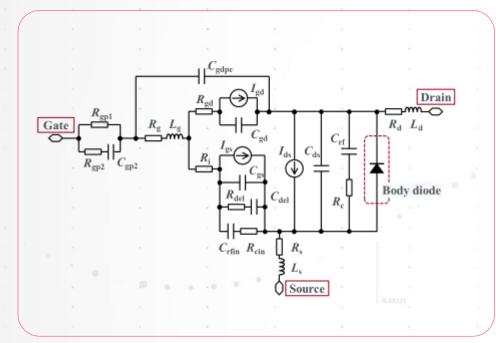

## What are different? (1)

#### **DEVICE MODEL**

Added body diode to better fit to SiC

$$\tanh\left(\left(\text{Lambda1} \times \tanh\left(1 + \text{Lambda2} \times V_{gs}\right)\right) \times V_{ds}\right)$$

Added Vgs, Vds dependent parameter to drain current equation to better represent unsaturated drain current

$$Q_{gs}$$

=  $(C_{gspi} + C_{gs0} \times \tanh 02)$

+  $(C_{gspi} + (C_{gs0} \times \tanh 01 + C_{gs0i} \times \tanh 1i) \times \tanh 02)$

$\tanh XX(i) = 1 + \tanh(A + B \times V_{gs} + C \times V_{ds})$

Added tanhXX to express a positive bias dependence on charge equation

- Modified popular Angelov GaN

- To represent SiC or GaN behavior better

- Independent of device physics parameters (e.g. Tox) → Everyone (e.g. circuit designer) can use it

Source: "Measurement Methodology for Accurate Modeling of SiC MOSFET Switching Behavior over Wide Voltage and Current Ranges", H. Sakairi, et. al., IEEE Trans on Power Electronics early access,

Keysight World

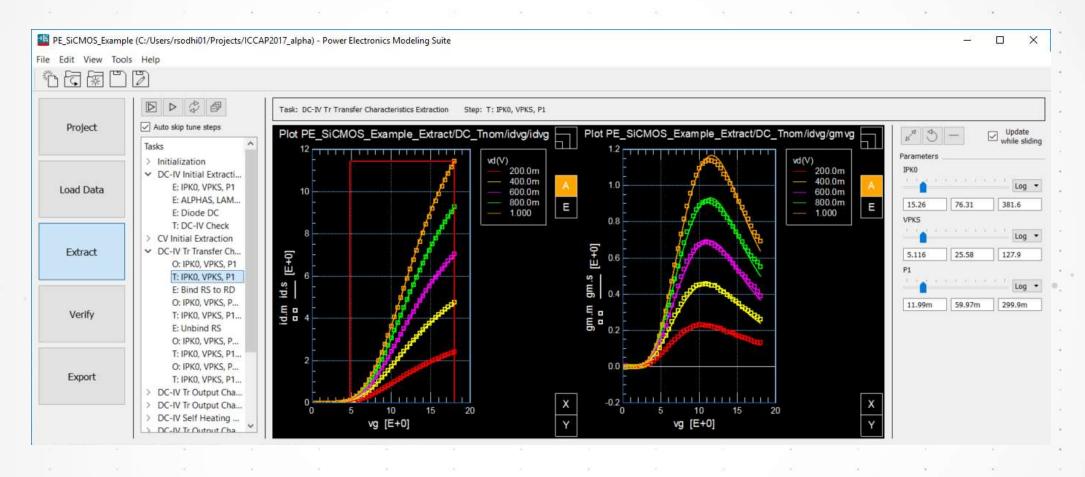

## **Power Electronics Model Generator**

Powerful flow dynamically adapts to measured data and provides turns-key automated extraction of Power Electronics models

## What are different? (2)

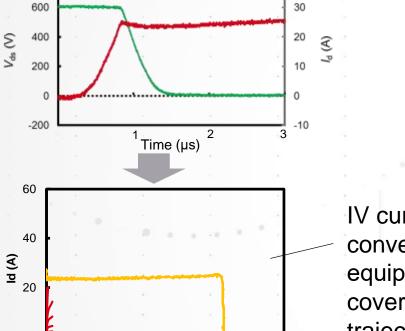

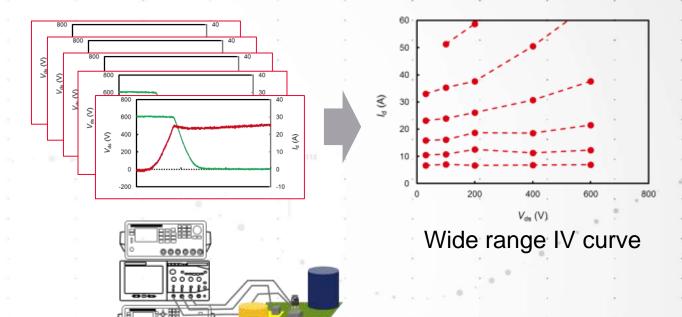

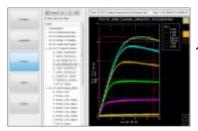

(A) Wide range IV using double pulse test

600

800

IV curve with conventional test equipment doesn't cover switching trajectory

Utilize double pulse test system to obtain wide enough IV curve to cover switching trajectory

Source: Measurement Measurement and a second of the Mark Source and Carlotte and Ca

200

400

Vds (V)

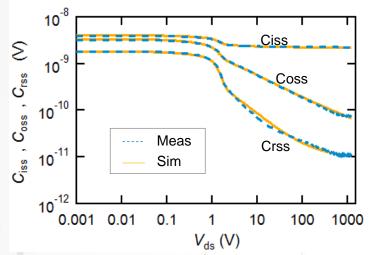

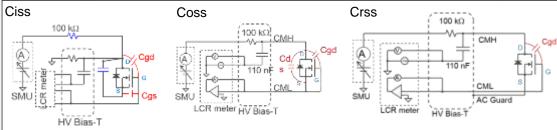

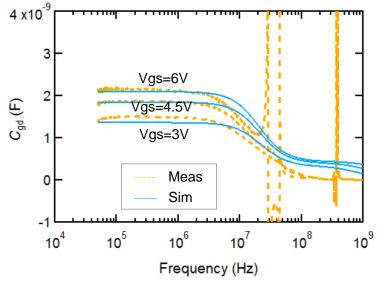

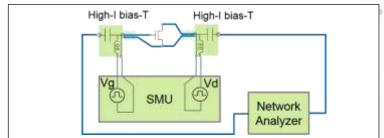

## What are different? (3)

(B) Inclusion of CV (both off-state & on-state)

Discontinuous measurement points seen beyond 10MHz are considered to be caused by oscillation due to parasitic and stray inductance associated with measurement circuit. Therefore, simulation didn't include those points.

Inclusion of non-linear characteristics is critical to represent device physical phenomena better

Source: "Measurement Methodology for Accurate Modeling of SiC MOSFET Switching Behavior over Wide Voltage and Current Ranges", H. Sakairi, et. al., IEEE Trans on Power Electronics early access,

Keysight World

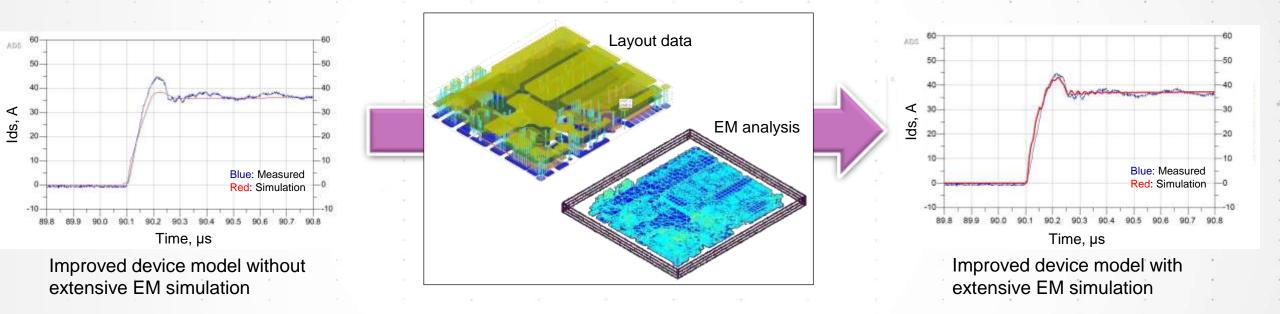

## What are different? (4)

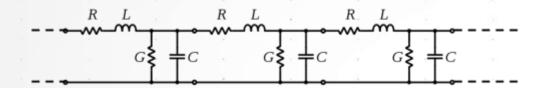

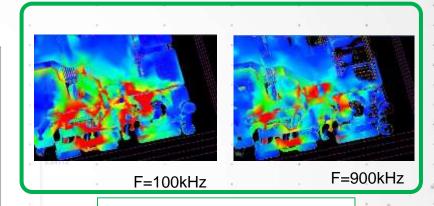

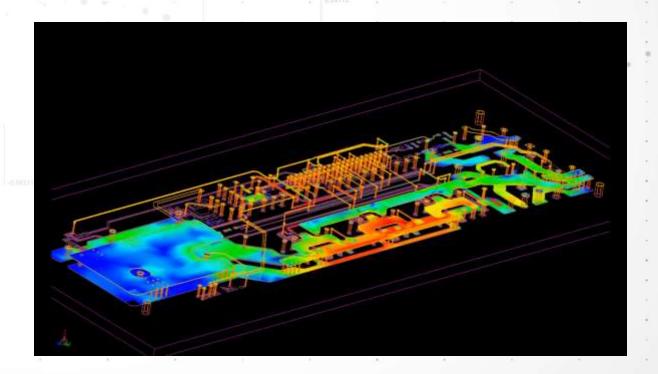

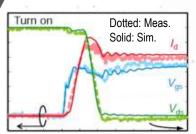

To use simulation software that performs not only time domain analysis but also incorporate electro-thermal and layout distribution effects

Electromagnetic simulation using board layout information as well as inclusion of s-parameters measured on DUT, the simulation of circuit operation becomes significantly better.

## Circuit simulation based on the model and

electromagnetic analysis

Conventional

#### New method

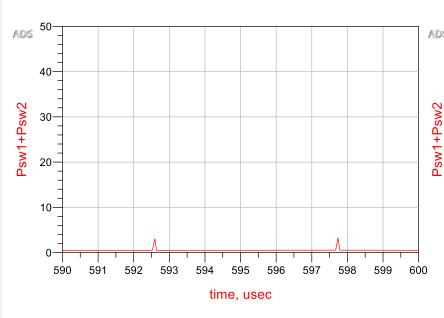

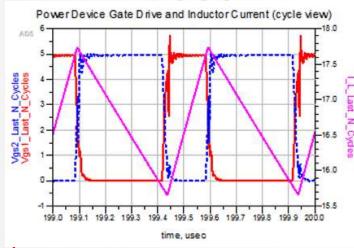

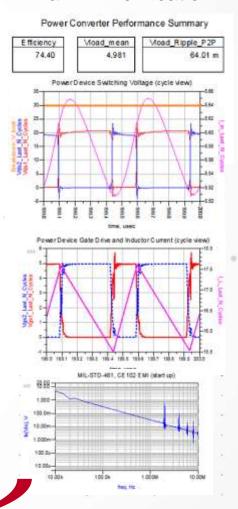

## **Results from EM-circuit Co-simulation**

EM-model informs the circuit simulation

Circuit excitation informs the EM postsimulation visualization display

Keysight World

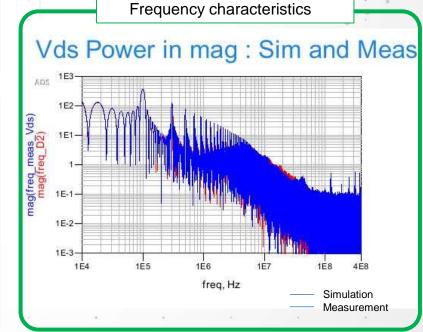

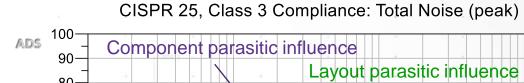

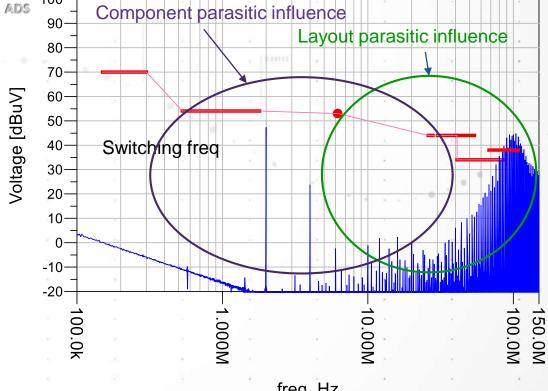

## Insights Given From the Simulated Spectrum

#### LAYOUT RELATED NOISE IS GREATER AT FM BAND

#### Underlying EMI mechanisms:

- Harmonically related components

- Non-harmonic related ringing

- Instabilities

- L di/dt mechanisms

#### Component and layout parasitics:

- Prevent EMI from being suppressed they always need to be modeled

- May create noise in different frequency spectrums

freq, Hz

## **Enabling technology**

Exact waveform match is critical for noise calculation as waveform contains high frequency components

Source: "Measurement Methodology for Accurate Modeling of SiC MOSFET Switching Behavior over Wide Voltage and Current Ranges", H. Sakairi, et. al., IEEE Trans on Power Electronics early access,

Keysight World

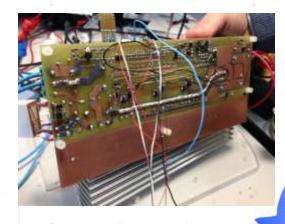

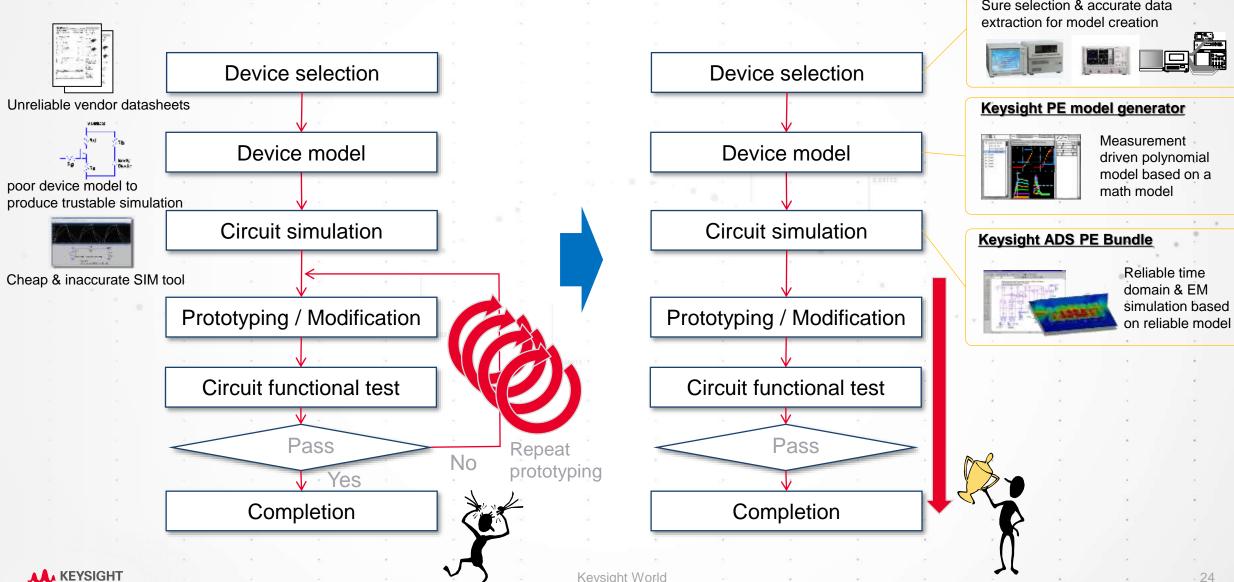

## **Before & After Our Solution**

#### **Keysight instruments**

Sure selection & accurate data

## **Keysight Integrated Power Electronics Solution**

## ADVANCED DESIGN SYSTEM (ADS)

**Power Electronics Library**

## W2240 Power Electronics Bundle **Schematic** 3D viewer Layout Momentum Transient/convolution **FEM** PWMD1 Freq=1 MHz

Data display

Verilog-A

## **Product Options**

W2300 Harmonic Balance Simulator

W2349 Electro-Thermal Simulator

## **Keysight Solutions for Power Electronics**

#### **KEY CHALLENGES OUR CUSTOMERS ARE FACING TODAY**

#### **Device Modeling**

#### **Device Parameter Measurement**

IATF Compliant Cal

B1506A Curve Tracer / Power **Device Analyzer** I-V. C-V

Double Pulse Test PD1500A High power I-V

E5080A ENA + Fixture Zero-bias S-param, On-state C-V

#### **Parameter Extraction**

**Power Electronics Model Generator** Simple and quick fitting

- 2. IC-CAP based Power MOS/SiC/GaN/IGBT Modeling Opt.

- For professional, high accurate modeling

- 3. Keysight Modeling Service

#### PE Design Challenges

- Mitigate noise on Switching (← Reliability, EMI Standards) Surge Voltage, di/dt, Conductive noise

- Thermal design (← Reliability) Thermal distribution on PCB (Air flow is partially supported)

- Improve power efficiency (← Efficiency) Switching Losses, Conductive losses

#### Circuit Development

#### **Simulation Design**

Source: IEICE the 29th Workshop on Circuits and Systems

**ADS PE Bundle** De-fact standard circuit simulator considering

**Real Measurement**

IATF Compliant Cal

Oscilloscope Waveform analysis and debugging

#### Parasitic Effect Consideration

#### Packaged/Passive modeling

ADS Full 3D EM/EMPro EM based simulation

**KEYSIGHT**

**Network Analyzer** Verification of devices

#### **Board Pattern Modeling**

ADS 3D-Planar EM Sim. Allows the most accurate design